初学者应该掌握的Verilog编程基础知识

Verilog是一种硬件描述语言,广泛应用于数字电路设计及验证。本文将介绍初学者应该掌握的Verilog编程基础知识,包括模块化设计、数据类型、流程控制、测试和调试等方面。

一、模块化设计

在Verilog中,模块是最基本的单元。模块可以嵌套、实例化,并且可以在模块内部或者外部声明。通常情况下,每个模块都有输入和输出端口,用于与其他模块或者外部信号进行交互。

例如,下面是一个简单的模块,用于实现一个简单的两位加法:

```verilog

module adder2(input [1:0] a, input [1:0] b, output [2:0] sum);

assign sum = a b;

endmodule

```

在这个例子中,我们定义了一个名为adder2的模块,并且规定了三个输入参数a和b以及一个输出参数sum。模块的功能很简单,就是将输入的a和b相加,然后将结果输出到sum端口。

二、数据类型

在Verilog中,有以下几种基本数据类型:

1. 位(bit):表示一个二进制数字,只能取0或者1。

2. 向量(vector):表示多个位,可以是连续的,也可以是不连续的。

3. 整数(integer):类似于C语言中的整型数据。

4. 实数(real):类似于C语言中的浮点型数据。

5. 字符串(string):表示多个字符。

6. 时间(time):表示一段时间的长度。

例如,下面是一个使用vector和integer数据类型的例子,用于实现一个简单的计数器:

```verilog

module counter(input clk, input reset, output reg [7:0] count);

always @(posedge clk or posedge reset) begin

if(reset)

count <= 8'h00;

else

count <= count 1;

end

endmodule

```

在这个例子中,我们定义了一个名为counter的模块,并且规定了三个输入参数clk和reset以及一个输出参数count。模块的功能是实现一个8位计数器,每当时钟信号上升沿到来时,计数器的值就会加1,当reset信号为高时,计数器的值将被重置为0。

三、流程控制

在Verilog中,流程控制语句包括ifelse、case、for、while等。这些语句可以帮助我们控制程序的执行流程,实现复杂的功能。

例如,下面是一个使用ifelse流程控制语句的例子,用于判断一个数是否为奇数:

```verilog

module odd(input [7:0] num, output reg is_odd);

always @(*) begin

if(num%2 == 1)

is_odd <= 1'b1;

else

is_odd <= 1'b0;

end

endmodule

```

在这个例子中,我们定义了一个名为odd的模块,并且规定了两个输入参数num以及一个输出参数is_odd。模块的功能是判断num是否为奇数,如果是,is_odd变量将为1,否则为0。

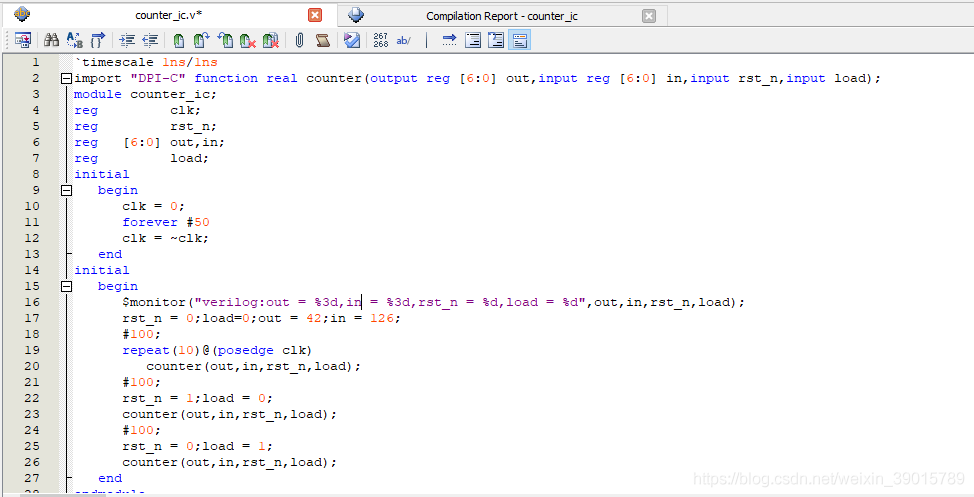

四、测试和调试

在Verilog中,我们一般使用仿真工具来测试我们的代码,比如ModelSim、Xilinx ISE等工具。仿真可以帮助我们验证我们的代码是否正确,并帮助我们调试代码。

例如,我们可以使用以下的Testbench来仿真前面提到的两个模块:

```verilog

module adder2_tb;

版权声明

本文仅代表作者观点,不代表百度立场。

本文系作者授权百度百家发表,未经许可,不得转载。